File Formats¶

VPR consumes and produces several files representing the packing, placement, and routing results.

FPGA Architecture (.xml)¶

The target FPGA architecture is specified as an architecture file. For details of this file format see FPGA Architecture Description.

BLIF Netlist (.blif)¶

The technology mapped circuit to be implement on the target FPGA is specified as a Berkely Logic Interchange Format (BLIF) netlist.

The netlist must be flattened and consist of only primitives (e.g. .names, .latch, .subckt).

For a detailed description of the BLIF file format see the BLIF Format Description.

Note that VPR supports only the structural subset of BLIF, and does not support the following BLIF features:

Subfile References (

.search).Finite State Machine Descriptions (

.start_kiss,.end_kissetc.).Clock Constraints (

.cycle,.clock_event).Delay Constraints (

.delayetc.).

Clock and delay constraints can be specified with an SDC File.

Note

By default VPR assumes file with .blif are in structural BLIF format. The format can be controlled with vpr --circuit_format.

Black Box Primitives¶

Black-box architectural primitives (RAMs, Multipliers etc.) should be instantiated in the netlist using BLIF’s .subckt directive.

The BLIF file should also contain a black-box .model definition which defines the input and outputs of each .subckt type.

VPR will check that blackbox .models are consistent with the <models> section of the architecture file.

Unconnected Primitive Pins¶

Unconnected primitive pins can be specified through several methods.

The

unconnnet (input pins only).VPR treats any input pin connected to a net named

unconnas disconnected.For example:

.names unconn out 0 1

specifies an inverter with no connected input.

Note

unconnshould only be used for input pins. It may cause name conflicts and create multi-driven nets if used with output pins.Implicitly disconnected

.subcktpins.For

.subcktinstantiations VPR treats unlisted primitive pins as implicitly disconnected. This works for both input and output pins.For example the following

.subcktinstantiations are equivalent:.subckt single_port_ram \ clk=top^clk \ data=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~546 \ addr[0]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~541 \ addr[1]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~542 \ addr[2]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~543 \ addr[3]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~544 \ addr[4]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~545 \ addr[5]=unconn \ addr[6]=unconn \ addr[7]=unconn \ addr[8]=unconn \ addr[9]=unconn \ addr[10]=unconn \ addr[11]=unconn \ addr[12]=unconn \ addr[13]=unconn \ addr[14]=unconn \ we=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~554 \ out=top.memory_controller+memtroll.single_port_ram+str^out~0.subckt single_port_ram \ clk=top^clk \ data=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~546 \ addr[0]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~541 \ addr[1]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~542 \ addr[2]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~543 \ addr[3]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~544 \ addr[4]=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~545 \ we=top.memory_controller+memtroll^MULTI_PORT_MUX~8^MUX_2~554 \ out=top.memory_controller+memtroll.single_port_ram+str^out~0Dummy nets with no sinks (output pins only)

By default VPR sweeps away nets with no sinks (see

vpr --sweep_dangling_nets). As a result output pins can be left ‘disconnected’ by connecting them to dummy nets.For example:

.names in dummy_net1 0 1

specifies an inverter with no connected output (provided

dummy_net1is connected to no other pins).Note

This method requires that every disconnected output pin should be connected to a uniquely named dummy net.

BLIF File Format Example¶

The following is an example BLIF file. It implements a 4-bit ripple-carry adder and some simple logic.

The main .model is named top, and its input and output pins are listed using the .inputs and .outputs directives.

The 4-bit ripple-cary adder is built of 1-bit adder primitives which are instantiated using the .subckt directive.

Note that the adder primitive is defined as its own .model (which describes its pins), and is marked as .blackbox to indicate it is an architectural primitive.

The signal all_sum_high_comb is computed using combinational logic (.names) which ANDs all the sum bits together.

The .latch directive instantiates a rising-edge (re) latch (i.e. an edge-triggered Flip-Flop) clocked by clk.

It takes in the combinational signal all_sum_high_comb and drives the primary output all_sum_high_reg.

Also note that the last .subckt adder has it’s cout output left implicitly disconnected.

.model top

.inputs clk a[0] a[1] a[2] a[3] b[0] b[1] b[2] b[3]

.outputs sum[0] sum[1] sum[2] sum[3] cout all_sum_high_reg

.names gnd

0

.subckt adder a=a[0] b=b[0] cin=gnd cout=cin[1] sumout=sum[0]

.subckt adder a=a[1] b=b[1] cin=cin[1] cout=cin[2] sumout=sum[1]

.subckt adder a=a[2] b=b[2] cin=cin[2] cout=cin[3] sumout=sum[2]

.subckt adder a=a[3] b=b[3] cin=cin[3] sumout=sum[3]

.names sum[0] sum[1] sum[2] sum[3] all_sum_high_comb

1111 1

.latch all_sum_high_comb all_sum_high_reg re clk 0

.end

.model adder

.inputs a b cin

.outputs cout sumout

.blackbox

.end

BLIF Naming Convention¶

VPR follows a naming convention to refer to primitives and pins in the BLIF netlist. These names appear in the VPR GUI, in log and error messages, and in can be used elsewhere (e.g. in SDC constraints).

Net Names¶

The BLIF format uses explicit names to refer to nets. These names are used directly as is by VPR (although some nets may be merged/removed by netlist cleaning).

For example, the following netlist:

.model top

.inputs a b

.outputs c

.names a b c

11 1

.end

contains nets named:

abc

Primitive Names¶

The standard BLIF format has no mechanism for specifying the names of primitives (e.g. .names/.latch/.subckt).

As a result, tools processing BLIF follow a naming convention which generates unique names for each netlist primitive.

The VPR primitive naming convention is as follows:

Primitive |

Drives at least one net? |

Primitive Name |

|---|---|---|

|

Yes |

Name of first driven net |

No |

Arbitrarily

generated (e.g.

|

|

|

N/A |

.output name

prefixed with

|

which ensures each netlist primitive is given a unique name.

For example, in the following:

.model top

.inputs a b x y z clk

.outputs c c_reg cout[0] sum[0]

.names a b c

11 1

.latch c c_reg re clk 0

.subckt adder a=x b=y cin=z cout=cout[0] sumout=sum[0]

.end

.model adder

.inputs a b cin

.outputs cout sumout

.blackbox

.end

The circuit primary inputs (

.inputs) are named:a,b,x,y,z,clk,The 2-LUT (

.names) is namedc,The FF (

.latch) is namedc_reg,The

adder(.subckt) is namedcout[0](the name of the first net it drives), andThe circuit primary outputs (

.outputs) are named:out:c,out:c_reg,out:cout[0],out:sum[0].

See also

EBLIF’s .cname extension, which allows explicit primitive names to be specified.

Pin Names¶

It is useful to be able to refer to particular pins in the netlist.

VPR uses the convention: <primitive_instance_name>.<pin_name>.

Where <primitive_instance_name> is replaced with the netlist primitive name, and <pin_name> is the name of the relevant pin.

For example, the following adder:

.subckt adder a=x b=y cin=z cout=cout[0] sumout=sum[0]

which has pin names:

cout[0].a[0](driven by netx)cout[0].b[0](driven by nety)cout[0].cin[0](driven by netz)cout[0].cout[0](drives netcout[0])cout[0].sumout[0](drives netsum[0])

Since the primitive instance itself is named cout[0] by convention.

Built-in Primitive Pin Names¶

The built-in primitives in BLIF (.names, .latch) do not explicitly list the names of their input/output pins.

VPR uses the following convention:

Primitive |

Port |

Name |

|---|---|---|

|

input |

|

output |

|

|

|

input |

|

output |

|

|

control |

|

Consider the following:

.names a b c d e f

11111 1

.latch g h re clk 0

The .names’ pin names are:

f.in[0](driven by neta)f.in[1](driven by netb)f.in[2](driven by netc)f.in[3](driven by netd)f.in[4](driven by nete)f.out[0](drives netf)

and the .latch pin names are:

h.D[0](driven by netg)h.Q[0](drives neth)h.clk[0](driven by netclk)

since the .names and .latch primitives are named f and h by convention.

Note

To support pins within multi-bit ports unambiguously, the bit index of the pin within its associated port is included in the pin name (for single-bit ports this will always be [0]).

Extended BLIF (.eblif)¶

VPR also supports several extentions to structural BLIF to address some of its limitations.

Note

By default VPR assumes file with .eblif are in extneded BLIF format. The format can be controlled with vpr --circuit_format.

.conn¶

The .conn statement allows direct connections between two wires.

For example:

.model top

.input a

.output b

#Direct connection

.conn a b

.end

specifies that ‘a’ and ‘b’ are direct connected together.

This is analogous to Verilog’s assign b = a;.

This avoids the insertion of a .names buffer which is required in standard BLIF, for example:

.model top

.input a

.output b

#Buffer LUT required in standard BLIF

.names a b

1 1

.end

.cname¶

The .cname statement allows names to be specified for BLIF primitives (e.g. .latch, .names, .subckt).

Note

.cname statements apply to the previous primitive instantiation.

For example:

.names a b c

11 1

.cname my_and_gate

Would name of the above .names instance my_and_gate.

.param¶

The .param statement allows parameters (e.g. primitive modes) to be tagged on BLIF primitives.

Note

.param statements apply to the previous primitive instantiation.

For example:

.subckt dsp a=a_in b=b_in cin=c_in cout=c_out s=sum_out

.param mode adder

Would set the parameter mode of the above dsp .subckt to adder.

.param statements propagate to <parameter> elements in the packed netlist.

.attr¶

The .attr statement allows attributes (e.g. source file/line) to be tagged on BLIF primitives.

Note

.attr statements apply to the previous primitive instantiation.

For example:

.latch a_and_b dff_q re clk 0

.attr src my_design.v:42

Would set the attribute src of the above .latch to my_design.v:42.

.attr statements propagate to <attribute> elements in the packed netlist.

Extended BLIF File Format Example¶

.model top

.inputs a b clk

.outputs o_dff

.names a b a_and_b

11 1

.cname lut_a_and_b

.param test_names_param "test_names_param_value"

.attr test_names_attrib "test_names_param_attrib"

.latch a_and_b dff_q re clk 0

.cname my_dff

.param test_latch_param "test_latch_param_value"

.attr test_latch_attrib "test_latch_param_attrib"

.conn dff_q o_dff

.end

Timing Constraints (.sdc)¶

Timing constraints are specified using SDC syntax. For a description of VPR’s SDC support see SDC Commands.

Note

Use vpr --sdc_file to specify the SDC file used by VPR.

Timing Constraints File Format Example¶

See SDC Examples.

Packed Netlist Format (.net)¶

The circuit .net file is an xml file that describes a post-packed user circuit. It represents the user netlist in terms of the complex logic blocks of the target architecture. This file is generated from the packing stage and used as input to the placement stage in VPR.

The .net file is constructed hierarchically using block tags.

The top level block tag contains the I/Os and complex logic blocks used in the user circuit.

Each child block tag of this top level tag represents a single complex logic block inside the FPGA.

The block tags within a complex logic block tag describes, hierarchically, the clusters/modes/primitives used internally within that logic block.

A block tag has the following attributes:

nameA name to identify this component of the FPGA. This name can be completely arbitrary except in two situations. First, if this is a primitive (leaf) block that implements an atom in the input technology-mapped netlist (eg. LUT, FF, memory slice, etc), then the name of this block must match exactly with the name of the atom in that netlist so that one can later identify that mapping. Second, if this block is not used, then it should be named with the keyword open. In all other situations, the name is arbitrary.

instanceThe phyiscal block in the FPGA architecture that the current block represents. Should be of format: architecture_instance_name[instance #]. For example, the 5th index BLE in a CLB should have

instance="ble[5]"

modeThe mode the block is operating in.

A block connects to other blocks via pins which are organized based on a hierarchy. All block tags contains the children tags: inputs, outputs, clocks. Each of these tags in turn contain port tags. Each port tag has an attribute name that matches with the name of a corresponding port in the FPGA architecture. Within each port tag is a list of named connections where the first name corresponds to pin 0, the next to pin 1, and so forth. The names of these connections use the following format:

Unused pins are identified with the keyword open.

The name of an input pin to a complex logic block is the same as the name of the net using that pin.

The name of an output pin of a primitve (leaf block) is the same as the name of the net using that pin.

The names of all other pins are specified by describing their immediate drivers. This format is

[name_of_immediate_driver_block].[port_name][pin#]->interconnect_name.

For primitives with equivalent inputs VPR may rotate the input pins.

The resulting rotation is specified with the <port_rotation_map> tag.

For example, consider a netlist contains a 2-input LUT named c, which is implemented in a 5-LUT:

1 2 3 4 5 6 7 8 9 10 11 12 13 | ...

<block name="c" instance="lut[0]">

<inputs>

<port name="in">open open lut5.in[2]->direct:lut5 open lut5.in[4]->direct:lut5 </port>

<port_rotation_map name="in">open open 1 open 0 </port_rotation_map>

</inputs>

<outputs>

<port name="out">c </port>

</outputs>

<clocks>

</clocks>

</block>

...

|

In the original netlist the two LUT inputs were connected to pins at indicies 0 and 1 (the only input pins).

However during clustering the inputs were rotated, and those nets now connect to the pins at indicies 2 and 4 (line 4).

The <port_rotation_map> tag specified the port name it applies to (name attribute), and its contents lists the pin indicies each pin in the port list is associated with in the original netlist (i.e. the pins lut5.in[2]->direct:lut5 and lut5.in[4]->direct:lut5 respectively correspond to indicies 1 and 0 in the original netlist).

Note

Use vpr --net_file to override the default net file name.

Packing File Format Example¶

The following is an example of what a .net file would look like. In this circuit there are 3 inputs (pa, pb, pc) and 4 outputs (out:pd, out:pe, out:pf, out:pg). The io pad is set to inpad mode and is driven by the inpad:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 | <block name="b1.net" instance="FPGA_packed_netlist[0]">

<inputs>

pa pb pc

</inputs>

<outputs>

out:pd out:pe out:pf out:pg

</outputs>

<clocks>

</clocks>

<block name="pa" instance="io[0]" mode="inpad">

<inputs>

<port name="outpad">open </port>

</inputs>

<outputs>

<port name="inpad">inpad[0].inpad[0]->inpad </port>

</outputs>

<clocks>

<port name="clock">open </port>

</clocks>

<block name="pa" instance="inpad[0]">

<inputs>

</inputs>

<outputs>

<port name="inpad">pa </port>

</outputs>

<clocks>

</clocks>

<attributes>

<attribute name="vccio">3.3</attribute>

</attributes>

<parameters>

<parameter name="iostandard">LVCMOS33</parameter>

</parameters>

</block>

</block>

...

|

Placement File Format (.place)¶

The first line of the placement file lists the netlist (.net) and architecture (.xml) files used to create this placement. This information is used to ensure you are warned if you accidentally route this placement with a different architecture or netlist file later. The second line of the file gives the size of the logic block array used by this placement. All the following lines have the format:

block_name x y subblock_number

The block_name is the name of this block, as given in the input .net formatted netlist.

x and y are the row and column in which the block is placed, respectively.

Note

The blocks in a placement file can be listed in any order.

The subblock number is meaningful only for I/O pads.

Since we can have more than one pad in a row or column when io_rat is set to be greater than 1 in the architecture file, the subblock number specifies which of the several possible pad locations in row x and column y contains this pad.

Note that the first pads occupied at some (x, y) location are always those with the lowest subblock numbers – i.e. if only one pad at (x, y) is used, the subblock number of the I/O placed there will be zero.

For CLBs, the subblock number is always zero.

The placement files output by VPR also include (as a comment) a fifth field: the block number. This is the internal index used by VPR to identify a block – it may be useful to know this index if you are modifying VPR and trying to debug something.

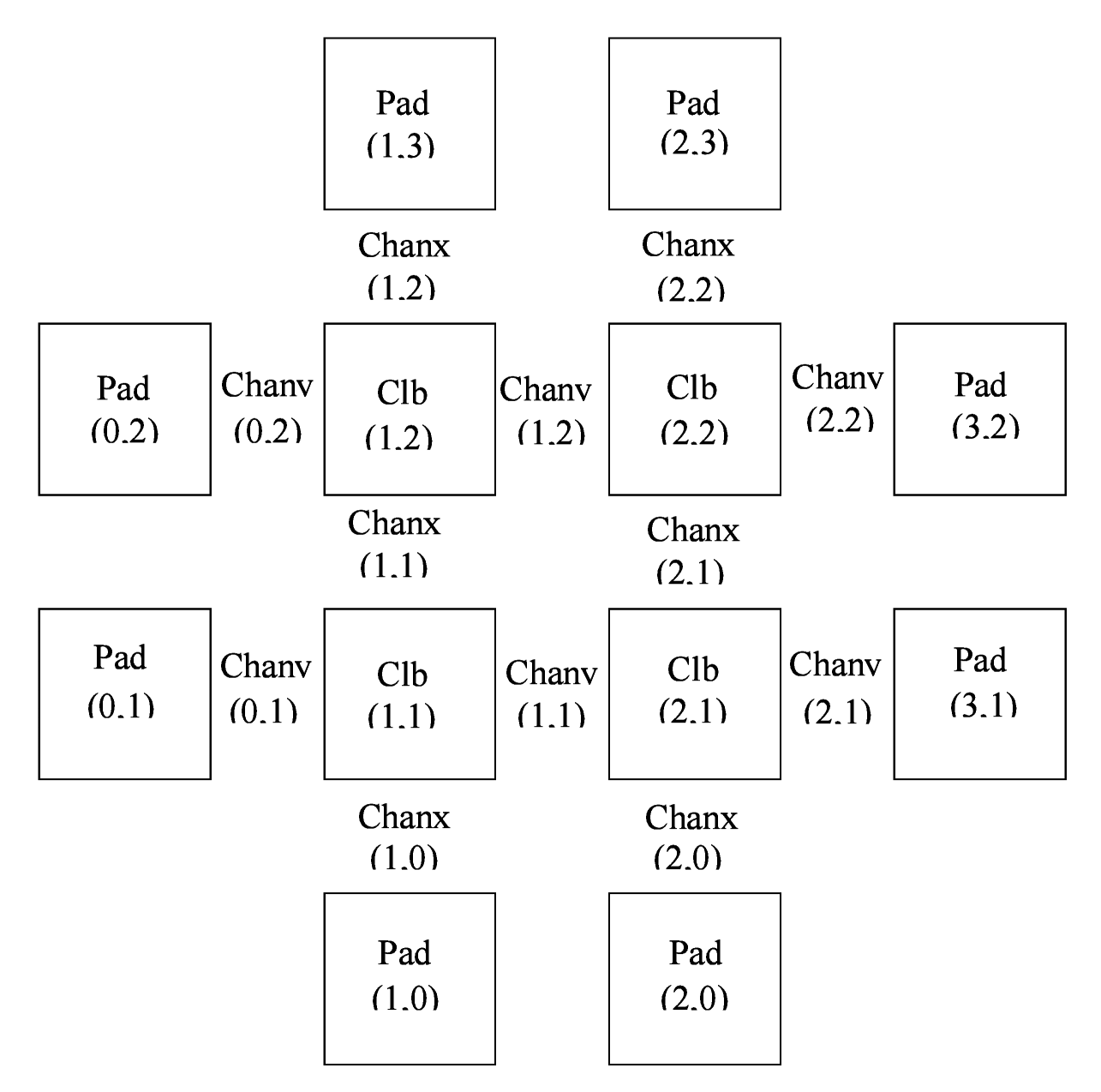

Fig. 3 FPGA co-ordinate system.¶

Fig. 3 shows the coordinate system used by VPR for a small 2 x 2 CLB FPGA.

The number of CLBs in the x and y directions are denoted by nx and ny, respectively.

CLBs all go in the area with x between 1 and nx and y between 1 and ny, inclusive.

All pads either have x equal to 0 or nx + 1 or y equal to 0 or ny + 1.

Note

Use vpr --place_file to override the default place file name.

Placement File Format Example¶

An example placement file is:

1 2 3 4 5 6 7 8 9 10 11 12 13 | Netlist file: xor5.net Architecture file: sample.xml

Array size: 2 x 2 logic blocks

#block name x y subblk block number

#---------- -- -- ------- -----------

a 0 1 0 #0 -- NB: block number is a comment.

b 1 0 0 #1

c 0 2 1 #2

d 1 3 0 #3

e 1 3 1 #4

out:xor5 0 2 0 #5

xor5 1 2 0 #6

[1] 1 1 0 #7

|

Routing File Format (.route)¶

The first line of the routing file gives the array size, nx x ny.

The remainder of the routing file lists the global or the detailed routing for each net, one by one.

Each routing begins with the word net, followed by the net index used internally by VPR to identify the net and, in brackets, the name of the net given in the netlist file.

The following lines define the routing of the net.

Each begins with a keyword that identifies a type of routing segment.

The possible keywords are SOURCE (the source of a certain output pin class), SINK (the sink of a certain input pin class), OPIN (output pin), IPIN (input pin), CHANX (horizontal channel), and CHANY (vertical channel).

Each routing begins on a SOURCE and ends on a SINK.

In brackets after the keyword is the (x, y) location of this routing resource.

Finally, the pad number (if the SOURCE, SINK, IPIN or OPIN was on an I/O pad), pin number (if the IPIN or OPIN was on a clb), class number (if the SOURCE or SINK was on a clb) or track number (for CHANX or CHANY) is listed – whichever one is appropriate.

The meaning of these numbers should be fairly obvious in each case.

If we are attaching to a pad, the pad number given for a resource is the subblock number defining to which pad at location (x, y) we are attached.

See Fig. 3 for a diagram of the coordinate system used by VPR.

In a horizontal channel (CHANX) track 0 is the bottommost track, while in a vertical channel (CHANY) track 0 is the leftmost track.

Note that if only global routing was performed the track number for each of the CHANX and CHANY resources listed in the routing will be 0, as global routing does not assign tracks to the various nets.

For an N-pin net, we need N-1 distinct wiring “paths” to connect all the pins.

The first wiring path will always go from a SOURCE to a SINK.

The routing segment listed immediately after the SINK is the part of the existing routing to which the new path attaches.

Note

It is important to realize that the first pin after a SINK is the connection into the already specified routing tree; when computing routing statistics be sure that you do not count the same segment several times by ignoring this fact.

Note

Use vpr --route_file to override the default route file name.

Routing File Format Examples¶

An example routing for one net is listed below:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 | Net 5 (xor5)

Node: 1 SOURCE (1,2) Class: 1 Switch: 1 # Source for pins of class 1.

Node: 2 OPIN (1,2) Pin: 4 clb.O[12] Switch:0 #Output pin the O port of clb block, pin number 12

Node: 4 CHANX (1,1) to (4,1) Track: 1 Switch: 1

Node: 6 CHANX (4,1) to (7,1) Track: 1 Switch: 1

Node: 8 IPIN (7,1) Pin: 0 clb.I[0] Switch: 2

Node: 9 SINK (7,1) Class: 0 Switch: -1 # Sink for pins of class 0 on a clb.

Node: 4 CHANX (7,1) to (10,1) Track: 1 Switch: 1 # Note: Connection to existing routing!

Node: 5 CHANY (10,1) to (10,4) Track: 1 Switch: 0

Node: 4 CHANX (10,4) to (13,4) Track: 1 Switch: 1

Node: 10 CHANX (13,4) to (16,4) Track: 1 Switch: 1

Node: 11 IPIN (16,4) Pad: 1 clb.I[1] Switch: 2

Node: 12 SINK (16,4) Pad: 1 Switch: -1 # This sink is an output pad at (16,4), subblock 1.

|

Nets which are specified to be global in the netlist file (generally clocks) are not routed. Instead, a list of the blocks (name and internal index) which this net must connect is printed out. The location of each block and the class of the pin to which the net must connect at each block is also printed. For clbs, the class is simply whatever class was specified for that pin in the architecture input file. For pads the pinclass is always -1; since pads do not have logically-equivalent pins, pin classes are not needed. An example listing for a global net is given below.

1 2 3 4 5 | Net 146 (pclk): global net connecting:

Block pclk (#146) at (1,0), pinclass -1

Block pksi_17_ (#431) at (3,26), pinclass 2

Block pksi_185_ (#432) at (5,48), pinclass 2

Block n_n2879 (#433) at (49,23), pinclass 2

|

Routing Resource Graph File Format (.xml)¶

The routing resource graph (rr graph) file is an XML file that describes the routing resources within the FPGA.

This file is generated through the last stage of the rr graph generation during routing with the final channel width.

When reading in rr graph from an external file, the rr graph is used during the placement and routing section of VPR.

The file is constructed using tags. The top level is the rr_graph tag.

This tag contains all the channel, switches, segments, block, grid, node, and edge information of the FPGA.

It is important to keep all the values as high precision as possible. Sensitive values include capacitance and Tdel. As default, these values are printed out with a precision of 30 digits.

Each of these sections are separated into separate tags as described below.

Note

Use vpr --read_rr_graph to specify an RR graph file to be load.

Note

Use vpr --write_rr_graph to specify where the RR graph should be written.

Top Level Tags¶

The first tag in all rr graph files is the <rr_graph> tag that contains detailed subtags for each catagory in the rr graph.

Each tag has their subsequent subtags that describes one entity. For example, <segments> includes all the segments in the graph where each <segment> tag outlines one type of segment.

The rr_graph tag contains the following tags:

<channels><channel>``content``</channel>

<switches><switch>``content``</switch>

<segments><segment>``content``</segment>

<block_types><block_type>``content``</block_type>

<grid><grid_loc>``content``</grid_loc>

<rr_nodes><node>``content``</node>

<rr_edges><edge>``content``</edge>

Note

The rr graph is based on the architecture, so more detailed description of each section of the rr graph can be found at FPGA architecture description

Detailed Tag Information¶

Channel¶

The channel information is contained within the channels subtag. This describes the minimum and maximum channel width within the architecture. Each channels tag has the following subtags:

Switches¶

A switches tag contains all the switches and its information within the FPGA. It should be noted that for values such as capacitance, Tdel, and sizing info all have high precision. This ensures a more accurate calculation when reading in the routing resource graph. Each switch tag has a switch subtag.

Segments¶

The segments tag contains all the segments and its information. Note again that the capacitance has a high decimal precision. Each segment is then enclosed in its own segment tag.

Blocks¶

The block_types tag outlines the information of a placeable complex logic block. This includes generation, pin classes, and pins within each block. Information here is checked to make sure it corresponds with the architecture. It contains the following subtags:

Grid¶

The grid tag contains information about the grid of the FPGA. Information here is checked to make sure it corresponds with the architecture. Each grid tag has one subtag as outlined below:

Nodes¶

The rr_nodes tag stores information about each node for the routing resource graph. These nodes describe each wire and each logic block pin as represented by nodes.

Edges¶

The final subtag is the rr_edges tag that encloses information about all the edges between nodes. Each rr_edges tag contains multiple subtags:

Node and Edge Metadata¶

metadata blocks (see Architecture metadata) are supported under both node and edge tags.

Routing Resource Graph Format Example¶

An example of what a generated routing resource graph file would look like is shown below:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 | <rr_graph tool_name="vpr" tool_version="82a3c72" tool_comment="Based on my_arch.xml">

<channels>

<channel chan_width_max="2" x_min="2" y_min="2" x_max="2" y_max="2"/>

<x_list index="1" info="5"/>

<x_list index="2" info="5"/>

<y_list index="1" info="5"/>

<y_list index="2" info="5"/>

</channels>

<switches>

<switch id="0" name="my_switch" buffered="1">

<timing R="100" Cin="1233-12" Cout="123e-12" Tdel="1e-9"/>

<sizing mux_trans_size="2.32" buf_size="23.54"/>

</switch>

</switches>

<segments>

<segment id="0" name="L4">

<timing R_per_meter="201.7" C_per_meter="18.110e-15"/>

</segment>

</segments>

<block_types>

<block_type id="0" name="io" width="1" height="1">

<pin_class type="input">

<pin ptc="0">DATIN[0]</pin>

<pin ptc="1">DATIN[1]</pin>

<pin ptc="2">DATIN[2]</pin>

<pin ptc="3">DATIN[3]</pin>

</pin_class>

<pin_class type="output">

<pin ptc="4">DATOUT[0]</pin>

<pin ptc="5">DATOUT[1]</pin>

<pin ptc="6">DATOUT[2]</pin>

<pin ptc="7">DATOUT[3]</pin>

</pin_class>

</block_type>

<block_type id="1" name="buf" width="1" height="1">

<pin_class type="input">

<pin ptc="0">IN</pin>

</pin_class>

<pin_class type="output">

<pin ptc="1">OUT</pin>

</pin_class>

</block_type>

</block_types>

<grid>

<grid_loc x="0" y="0" block_type_id="0" width_offset="0" height_offset="0"/>

<grid_loc x="1" y="0" block_type_id="1" width_offset="0" height_offset="0"/>

</grid>

<rr_nodes>

<node id="0" type="SOURCE" direction="NONE" capacity="1">

<loc xlow="0" ylow="0" xhigh="0" yhigh="0" ptc="0"/>

<timing R="0" C="0"/>

</node>

<node id="1" type="CHANX" direction="INC" capacity="1">

<loc xlow="0" ylow="0" xhigh="2" yhigh="0" ptc="0"/>

<timing R="100" C="12e-12"/>

<segment segment_id="0"/>

</node>

</rr_nodes>

<rr_edges>

<edge src_node="0" sink_node="1" switch_id="0"/>

<edge src_node="1" sink_node="2" switch_id="0"/>

</rr_edges>

</rr_graph>

|